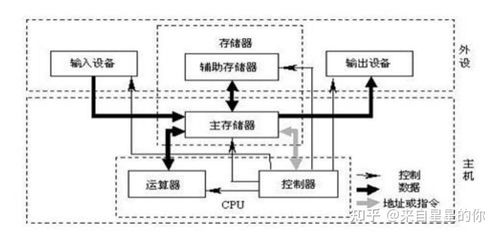

计算机的组成原理是现代信息技术的基础,其中主存储器(Main Memory)作为计算机硬件系统的核心组件之一,承担着程序与数据的临时存储任务。它与中央处理器(CPU)直接交互,是影响计算机整体性能的关键因素。与此在当今网络化的计算环境中,主存储器也与各类网络设备紧密协作,共同构成了高效、可靠的信息处理与传输体系。

一、主存储器的硬件组成

主存储器,通常指随机存取存储器(RAM),其硬件结构主要由以下几个部分构成:

- 存储体(Memory Bank/Cell Array):这是存储器的核心,由大量基本存储单元(Memory Cell)构成。每个存储单元通常由电容和晶体管组成(如在动态随机存取存储器DRAM中),能够存储一个二进制位(bit)。这些单元按矩阵形式排列,通过行地址和列地址进行寻址。

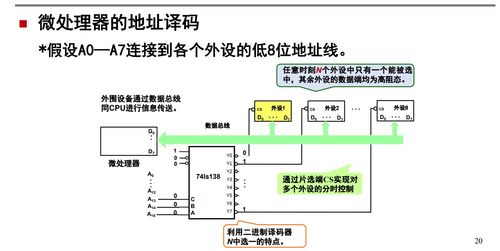

- 地址寄存器(Address Register, MAR)和地址译码器(Address Decoder):CPU或内存控制器将需要访问的存储单元地址送入地址寄存器。地址译码器则将该地址转换为对应存储单元的行选和列选信号,从而选中特定的存储单元。

- 数据寄存器(Data Register, MDR)/ 读写驱动器(Read/Write Drivers):在读取操作时,从被选中的存储单元中读出的微弱电信号经过放大后,暂存于数据寄存器,准备传送给CPU。在写入操作时,CPU要写入的数据首先送入数据寄存器,再由读写驱动器将其转换为足够的电平信号,写入到指定的存储单元中。

- 时序控制电路(Timing and Control Circuitry):负责产生和协调存储器内部各项操作(如预充电、行激活、列选通、读写等)所需的控制信号和时序,确保读写操作准确无误地按照规定的时钟周期完成。它接收来自内存控制器的命令(如读、写、刷新)。

- 刷新电路(Refresh Circuitry):对于DRAM,因其存储电容上的电荷会随时间泄漏,必须定期(通常每64ms)对所有存储单元进行刷新以保持数据。刷新电路负责生成刷新地址和控制信号,在不干扰正常读写操作的情况下完成刷新任务。

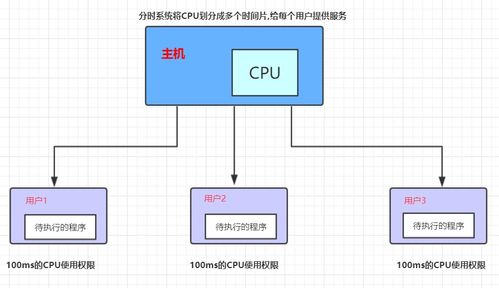

- 内存控制器(Memory Controller):通常位于计算机主板上的北桥芯片组或集成于CPU内部。它是CPU与主存之间的接口,负责管理内存的地址映射、访问时序、刷新调度以及错误校验(如ECC)等高级功能。

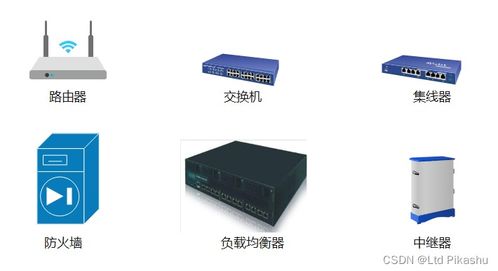

二、主存储器与网络设备的硬件关联

在联网的计算机系统中,主存储器不仅服务于本地CPU的计算任务,也与网络设备的协同工作息息相关。网络设备(如网卡NIC、路由器、交换机等)与主存的交互主要通过以下方式实现:

- 直接内存访问(DMA):这是关键机制。网络接口卡(NIC)通常具备DMA控制器。当有网络数据包到达或需要发送时,NIC的DMA控制器可以在不占用CPU资源的情况下,直接与主存储器进行数据交换。它将接收到的数据包直接写入主存中操作系统预先分配的缓冲区,或从主存的发送缓冲区直接读取数据包进行发送。这极大地减轻了CPU的负担,提高了网络吞吐率。

- 共享内存区域:操作系统会为核心网络协议栈(如TCP/IP协议栈)和网卡驱动程序在主存中划分专用的数据缓冲区(发送/接收缓冲区)。这些区域成为CPU(执行协议处理)和网络设备硬件之间共享的数据交换区。

- 对网络设备性能的影响:主存储器的性能(如带宽、延迟)直接影响网络数据处理的速度。高速的DDR4/DDR5内存能够更快地为网卡提供发送数据或接纳接收数据,减少数据在内存总线上的排队延迟,从而支持更高的网络速率(如万兆以太网)。

- 在网络设备内部的角色:高端路由器、交换机等网络设备本身也包含类似计算机的硬件体系,拥有自己的主存储器(通常是高性能的SRAM或DRAM)。这些内存用于存储转发表(FIB)、路由表、数据包缓冲区、队列管理信息等,是实现高速数据包转发和复杂网络策略的核心硬件资源。其容量和速度直接决定了设备的转发能力和并发连接数。

结论

计算机的主存储器是一个精密的硬件系统,由存储体、译码电路、控制电路等部件协同工作。在联网环境中,通过DMA等机制,主存储器与网络设备硬件形成了高效的数据通道,使得数据能在计算核心与网络之间流畅传输。理解主存储器的硬件组成及其与网络设备的交互,对于设计高性能计算系统、优化网络应用以及进行底层系统开发都具有重要意义。从单机到网络,主存储器始终是信息存储与流动的关键枢纽。